Herausforderungen für kryptografische Verfahren

In der digitalen Welt ist die Authentizität und Integrität von Daten essentiell. So soll beispielsweise sichergestellt werden, dass Firmware und Software auf einem Gerät aus einer vertrauenswürdigen Quelle stammen und nicht manipuliert oder ersetzt wurden. Dies geschieht meist über Signaturen, welche im Secure Boot Prozess während des Systemstarts überprüft werden. Der entsprechende Code wird nur ausgeführt, wenn die Prüfung erfolgreich war.

Um die Sicherheit der Daten und die Vertraulichkeit der Informationen zu gewährleisten, müssen kryptografische Verfahren wie Signaturen verschiedenen Angriffspfaden standhalten. Eine Prüfmethode ist die Kryptoanalyse, bei der aufgrund von mathematischen und statistischen Zusammenhängen der Ein- und Ausgangswerte eines Algorithmus Rückschlüsse auf den geheimen Schlüssel gezogen werden.

Ein Teilbereich der Kryptoanalyse sind potenzielle Angriffe mit Hilfe von Quantencomputern. Sie ermöglichen weitere krypto-analytische Angriffspfade, denn konventionelle Signaturverfahren basieren auf mathematischen Problemen, welche mit potenziell leistungsfähigen Quantencomputern gebrochen werden können. Die dafür benötigte Technologie befindet sich noch in der Entwicklung, aber es wird in Fachkreisen davon ausgegangen, dass dies in der näheren Zukunft signifikante Auswirkungen auf die IT-Sicherheit haben wird.

Deswegen werden aktuell große Bemühungen in der Entwicklung und Umsetzung quantensicherer Verfahren, auch als Post-Quanten-Kryptografie (PQC) bekannt, unternommen.

Das Fraunhofer AISEC leistet hier mit dem Kompetenzzentrum Post-Quanten-Kryptografie einen Beitrag zur Erforschung neuer quantenresistenter kryptografischer Verfahren.

Bei den auf dem WOTS-Verfahren basierenden Signaturverfahren, die in der Studie des Fraunhofer AISEC untersucht wurden, sind keine erfolgreichen Angriffe dieser Art bekannt.

Da sie allerdings besonders in eingebetteten Geräten zum Einsatz kommen, sind sie einem weiteren Angriffspfad ausgesetzt: den Hardware-Angriffen.

Diese Art der Angriffe zielt auf die konkrete Umsetzung des Algorithmus ab, also die Implementierung auf der konkreten Hardware. Dabei spielen die physischen Eigenschaften der Architektur und die Auswirkungen der Operationen eine wichtige Rolle. Von passivem Beobachten und Analysieren von Zwischenwerten bis hin zu invasiven Angriffen mit Manipulationen wie dem Überspringen von Operationen bestehen verschiedene Angriffsmöglichkeiten.

Studie zu Laser-basiertem Fehlerangriff auf XMSS

Die aktuelle Studie wurde im Auftrag des Bundesamts für Sicherheit in der Informationstechnik (BSI) am Fraunhofer AISEC durchgeführt. In diesem Rahmen wurde ein Laser-basierter Fehlerangriff auf das Signaturschema XMSS angewendet, mit dem die Authentizität und Integrität der Firmware quantensicher überprüft werden.

Das angegriffene quantensichere Signaturschema XMSS basiert auf dem WOTS-Verfahren, das auch anderen kryptografischen Signaturverfahren wie LMS und SPHINCS+ zugrunde liegt. Sowohl XMSS als auch WOTS verwenden Hash-Funktionen, um ihre Sicherheit zu gewährleisten. Dabei ist zu beachten, dass es sich um ein zustandsbehaftetes Signaturverfahren handelt. In der Praxis wird es hauptsächlich zur Verifikation von Daten verwendet, die sich selten ändern, wie beispielsweise beim Boot-Vorgang eines eingebetteten Systems.

Theoretische Vorarbeiten legen Grundstein für die Untersuchungen

Die aktuellen Arbeiten basieren auf einer Forschungsarbeit des Fraunhofer AISEC. Darin haben Alexander Wagner und seine Mitwirkenden gezeigt, wie ein Fehlerangriff auf ein hash-basiertes Signaturverfahren funktionieren kann.

Zum einen wurden Fehler in die Signaturerstellung eingebracht, um auf Teile des geheimen Schlüssels schließen zu können. Dadurch ist es Angreifenden möglich, gefälschte Signaturen zu erstellen, die einer Überprüfung standhalten.

Zum anderen wurden Fehler in die Signaturprüfung eingebracht, um zu verhindern, dass eine gefälschte Signatur als nicht echt erkannt wird. In der nun vom BSI veröffentlichten Studie wurde der zweite Angriff in der Praxis demonstriert.

Fehlerangriffe verändern Zwischenwerte und stören die Berechnungen

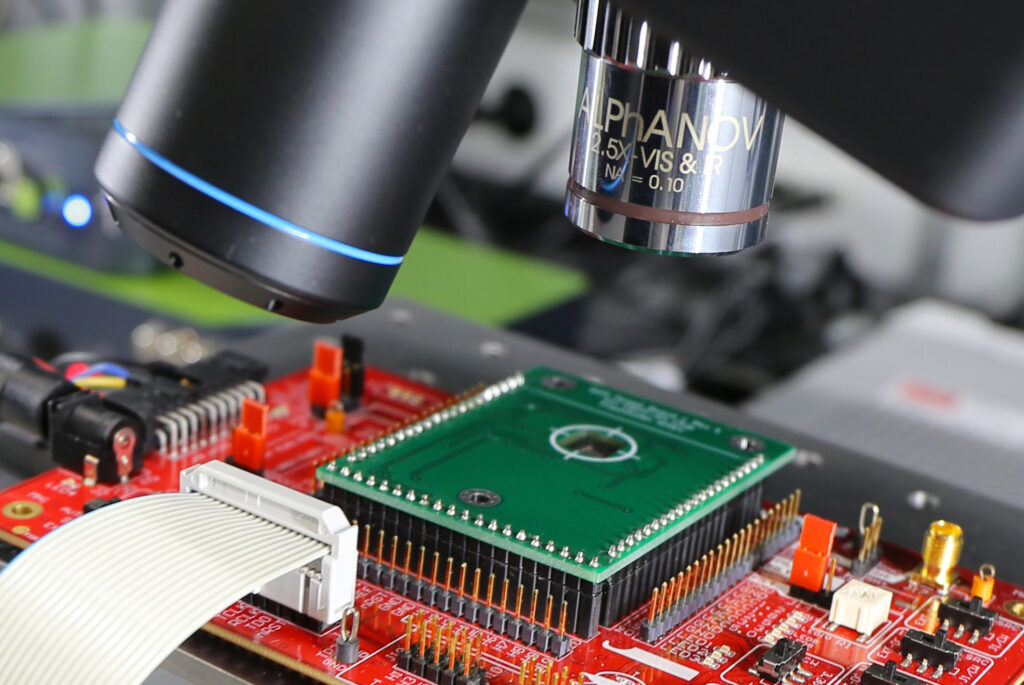

Im Rahmen des Projekts wurde ein aktiver Seitenkanalangriff an einem Standard-Mikrocontroller gezeigt.

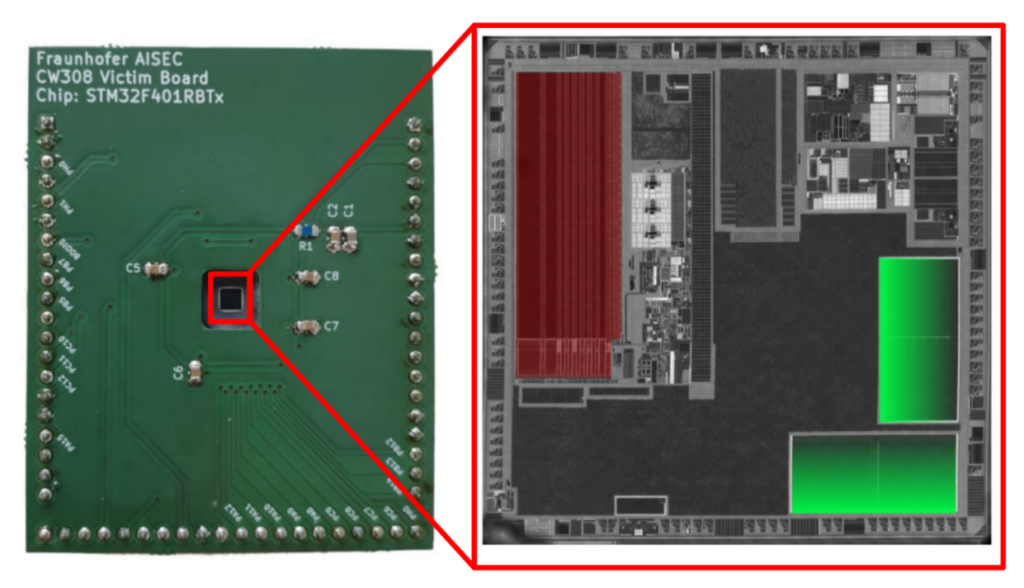

Im ersten Schritt wurde dafür das Target vorbereitet und genauer analysiert. Mit Hilfe von Infrarotaufnahmen des Chips konnten die relevanten Zonen für einen Angriff erkannt werden. Mittels gezielter Laserpulse wurden Zwischenwerte im SRAM manipuliert, um das Berechnungsergebnis zu verändern. Durch Analyse der ausgelösten Fehler konnte ein Fehlermodell für den Chip entwickelt werden, um einen gezielten Wert zu verändern.

Anschließend wurde gezeigt, dass ein Fehler gezielt in die Berechnung der Checksumme – eine mathematische Prüfsumme zur Validierung der Datenintegrität innerhalb der Signatur – eingebracht werden kann, was zur Folge hat, dass eine gefälschte Signatur der Firmware als gültig eingestuft wird.

Im Vergleich zu anderen Arbeiten mit Laser-basierten Fehlerangriffen war das Zeitfenster für das Einbringen des Fehlers in diesem Angriffsmodell besonders groß.

Angriffe sollen Hersteller und Entwickler sensibilisieren

In den Arbeiten vom Fraunhofer AISEC werden gezielte Gegenmaßnahmen diskutiert und vorgeschlagen, welche einen solchen Angriffspfad unterbinden.

Eine Gegenmaßnahme mit im Verhältnis zur Gesamtrechendauer vernachlässigbarem Aufwand stellt die wiederholte Berechnung und Überprüfung der Checksumme dar. Mit Hilfe dieser leicht umzusetzenden Gegenmaßnahme werden Angriffe dieser Art bedeutend erschwert, da eine Manipulation der Checksumme erkannt wird.

Durch die Veröffentlichung wird ein breites Publikum über die Angriffe aufgeklärt.

Somit können Hersteller und Entwickler bereits in der Produktentwicklung derart potenzielle Schwachstellen erkennen und ausbessern.

Insgesamt legen diese Arbeiten einen wichtigen Grundstein für das Verständnis, wie Implementierungen von hash-basierten Signaturverfahren in der Praxis aussehen sollten.

Bilder

Abbildung 1: Mit Hilfe des ALPhANOV-Laseraufbaus werden kurze Laserpulse in das Target Device eingebracht, um Fehler in der Berechnung zu erzeugen.

Abbildung 2: Mit Hilfe einer Infrarotaufnahme des Target Chips können die Bereiche des Target Devices zugeordnet werden. Hier in Rot der Flash Speicher und in Grün der SRAM.

Autoren

Silvan Streit

Silvan Streit forscht seit 2019 als wissenschaftlicher Mitarbeiter am Fraunhofer AISEC in der Abteilung Hardware Security. Seine Kernkompetenz ist die Seitenkanalsicherheit von Post-Quanten-Kryptografie, mit besonderem Fokus auf die Entdeckung neuer Angriffsvektoren. Hierbei setzt er auf seine Vorkenntnisse in der Informationsfeldtheorie sowie in sicheren und effizienten Implementierungen von Gitterverfahren.

Kontakt: silvan.streit@aisec.fraunhofer.de

Marc Schink

Marc Schink forscht in der Abteilung Hardware Security am Fraunhofer AISEC. Sein Schwerpunkt liegt auf der Entdeckung von Schwachstellen in Hard- und Software. Dabei hat er bereits mehrere Schwachstellen-Meldungsverfahren zu Produkten namhafter nationaler und internationaler Hersteller durchgeführt.

Kontakt: marc.schink@aisec.fraunhofer.de

Alexander Wagner

Alexander Wagner ist seit 2018 wissenschaftlicher Mitarbeiter am Fraunhofer AISEC in der Abteilung Hardware Security. Seine Forschung konzentriert sich auf die sichere und effiziente Implementierung von hash-basierten Signaturverfahren. Außerdem beschäftigt er sich mit der Durchführung von Seitenkanalanalysen und Fehlerangriffen im Labor sowie deren Limitationen.

Kontakt: alexander.wagner@aisec.fraunhofer.de