Fraunhofer AISEC im Auftrag des BSI: Neue Studie zur Synthese von kryptografischen Hardware-Implementierungen

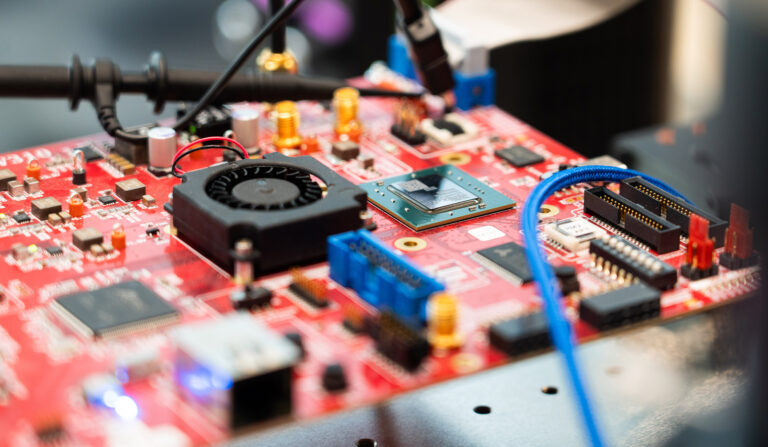

Die Studie des Fraunhofer AISEC zur Sicherheit kryptografischer Hardware-Implementierungen fokussiert Angriffe auf physische Hardware, wie Seitenkanalangriffe und Fehlerangriffe, sowie Maßnahmen zu deren Abwehr. Diese Schutzmechanismen können durch Optimierungen im Prozess des Chip-Designs potenziell Schaden nehmen. Die Untersuchung zeigt, dass Schutzmaßnahmen in komplexe Design-Abläufe integriert und bei der Hardware-Design-Synthese berücksichtigt werden sollten, um gegenüber Hardware-Angriffen resilient zu sein. Die Erkenntnisse nutzen Hardware-Designern bei der Entwicklung von robusten und sicheren Chips.